圖/宜特科技

圖/宜特科技

從小時候的底片相機,發展到數位相機,如今手機就能拍出許多高清又漂亮的照片,你知道都是多虧了CIS晶片嗎?

本文轉載自宜特小學堂《CIS晶片遇到異常 求助無門怎麼辦》,如果您對半導體產業新知有興趣,歡迎按下右邊的追蹤,就不會錯過宜特科技的最新文章!

CIS晶片又稱CMOS影像感測器(CMOS Image Sensor),最早是在1963年由美國一家半導體公司發明出來的積體電路設計,隨著時代進步,廣泛應用在數位攝影的感光元件中。而人們對攝影鏡頭解析度需求不斷增加,渴望拍出更精美的畫質。

CIS產就從早期數十萬像素,一路朝億級像素邁進,有賴於摩爾定律(Moore’s Law)在半導體微縮製程地演進,使得訊號處理能力顯著提升。如今的CIS已經不僅適用於消費型電子產品,在醫療檢測、安防監控領域等應用廣泛,近幾年智慧電車興起,先進駕駛輔助系統(ADAS, Advanced Driver. Assistance Systems)已成為新車的安全標配,未來車用CIS的市場更是潛力無窮。

然而,越精密、越高階的CIS晶片由於結構比較薄,加上特殊的3D堆疊結構,使得研發難度大大提升,當遇到異常(Defect)現象時,想透過分析找出故障的真因也更為困難了。

本文將帶大家認識三大晶片架構,並以案例說明當CIS晶片遇到異常,到底我們可以利用那些工具或手法,成功DEBUG?

一、認識CIS三大晶片架構

現今CIS晶片架構,可概分為三大類,(一)前照式 (Front Side illumination,簡稱FSI); (二)背照式 (Back Side illumination,簡稱BSI);(三) 堆疊式CIS (Stacked CIS):

(一) 前照式(FSI) CIS

為使CIS晶片能符合半導體製程導入量產,最初期的CIS晶片為前照式 (Front Side illumination,簡稱FSI) CIS;其感光路徑係透過晶片表面進行收光,不過,前照式CIS在效能上的最大致命傷為感光路徑會因晶片的感光元件上方金屬層干擾,而造成光感應敏度衰減。

(二) 背照式(BSI) CIS

為使CIS晶片能有較佳的光感應敏度,背照式 (Back Side illumination ,簡稱BSI) CIS技術應運而生。此類型產品的感光路徑,係由薄化至數微米後晶片背面進行收光,藉此大幅提升光感應能力。

而BSI CIS的前段製程與FSI CIS類似,主要差別在於後段晶片對接與薄化製程。BSI CIS的製程是在如同FSI CIS一般製程後,會將該CIS晶片正面與Carrier wafer對接。對接後的晶片再針對CIS晶片背面進行Backside grinding製程至數微米厚度以再增進收光效率,即完成BSI CIS。

(三) 堆疊式(Stacked) CIS

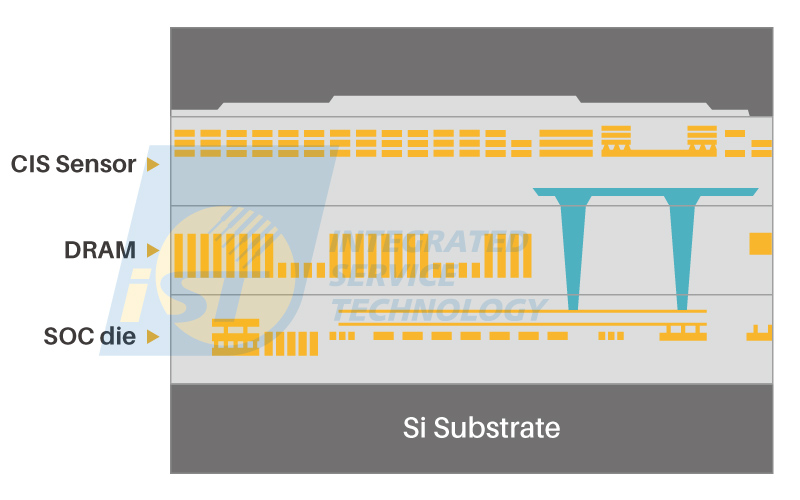

隨著智慧型手機等消費電子應用的蓬勃發展,人們對於拍攝影像的影像處理功能需求也大幅增加,使製作成本更親民與晶片效能更能有效提升,利用晶圓級堆疊技術,將較成熟製程製作的光感測元件 (Sensor Chip)晶片,與由先進製程製作、能提供更強大計算能力的特殊應用IC (Application Specific Integrated Circuit,簡稱ASIC) 晶片、或是再進一步與記憶體(DRAM)晶片進行晶圓級堆疊後,便可製作出兼具高效能與成本效益的堆疊式CIS (Stacked CIS)晶片(圖一),也是目前最主流的晶片結構。

《圖一》堆疊式(Stacked) CIS晶片示意圖。圖/宜特科技

《圖一》堆疊式(Stacked) CIS晶片示意圖。圖/宜特科技

二、如何找堆疊式(Stacked) CIS晶片的異常點(Defect)呢?

介紹完三大類CIS架構,我們就來進入本文重點:「如何找到堆疊式(Stacked) CIS晶片的異常點(Defect)?」

由於這類型的CIS晶片結構相對複雜,在進行破壞性分析前,需透過電路專家電路分析或熱點(Hot Spot)故障分析,鎖定目標、縮小範圍在 Stacked CIS晶片中的其一晶片後,針對可疑的失效點/失效層,進行該CIS樣品破壞性分析,方可有效地呈現失效點的失效狀態以進行進一步的預防修正措施。

接著,我們將分享宜特故障分析實驗室,是如何(一)利用電性熱點定位;(二)移除非鎖定目標之晶粒(Die),並針對鎖定目標晶粒(Die)逐層分析;(三)電性量測分析;(四)超音波顯微鏡(SAT)分析等四大分析手法交互應用,進行Stacked CIS晶片進行故障分析,順利找到異常點(Defect)。

(一) 透過電性熱點定位找故障點(Hot Spot)

當CIS晶片具有高阻值(High Resistance)、短路(Short)、漏電(Leakage)或是功能失效(Function Failure)等電性失效時,可依據不同的電性失效模式,經由直流通電或上測試板通電,並透過選擇適合的電性故障分析(EFA, Electrical Failure Analysis)工具來進行電性定位分析。

設備OBIRCHThermal EMMIInGaAs偵測目標電晶體/金屬層金屬層/封裝/印刷電路板電晶體/ 金屬層失效模式漏電/短路/高阻值漏電/短路/高阻值漏電/短路/開路各設備適合使用的選擇時機

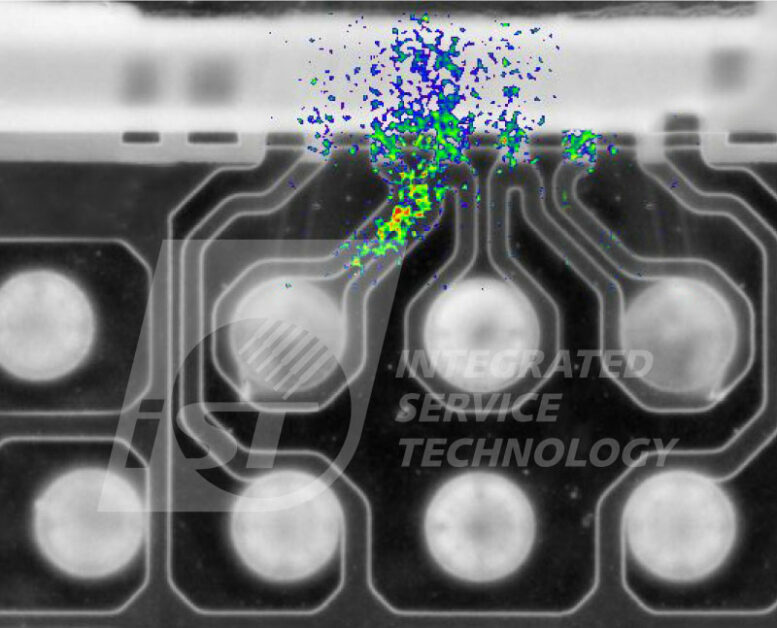

包括雷射光束電阻異常偵測(Optical Beam Induced Resistance Change,簡稱OBIRCH)、熱輻射異常偵測顯微鏡(Thermal EMMI)(圖二)、砷化鎵銦微光顯微鏡(InGaAs),藉由故障點定位設備找出可能的異常熱點(Hot Spot)位置,以利後續的物性故障(PFA, Physical Failure Analysis )分析。

《圖二》透過Thermal EMMI找到電性失效的故障點位置。圖/宜特科技

《圖二》透過Thermal EMMI找到電性失效的故障點位置。圖/宜特科技

(二) 移除非鎖定目標之晶粒,並針對鎖定目標晶粒逐層分析

接著,依照上述電性分析縮小可能的異常範圍至光感測元件晶片、ASIC或記憶體晶片區後,根據Stacked CIS晶片堆疊的結構特性,需先將其一側的矽基材移除,方可進行逐層去除(Layer by layer),或層層檢查。

再者,透過特殊分析手法,移除不需保留的晶粒結構,進而露出目標晶粒之最上層金屬層(圖三)。接著,透過逐層去除(Layer by layer),最終在金屬層第一層(Metal 1)找到燒毀現象的異常點(defect)(圖四)。

《圖三》搭配特殊手法,將CIS待測樣品不需保留之晶粒部分,完整移除。圖/宜特科技

《圖三》搭配特殊手法,將CIS待測樣品不需保留之晶粒部分,完整移除。圖/宜特科技

《圖四》對照Hot Spot分析範圍,進行鎖定目標晶粒進行逐層去除,發現燒毀現象。圖/宜特科技

《圖四》對照Hot Spot分析範圍,進行鎖定目標晶粒進行逐層去除,發現燒毀現象。圖/宜特科技

(三)電性量測分析:導電性原子力顯微鏡(C-AFM, Conductive Atomic Force Microscopy)與奈米探針系統(Nano-prober)的應用

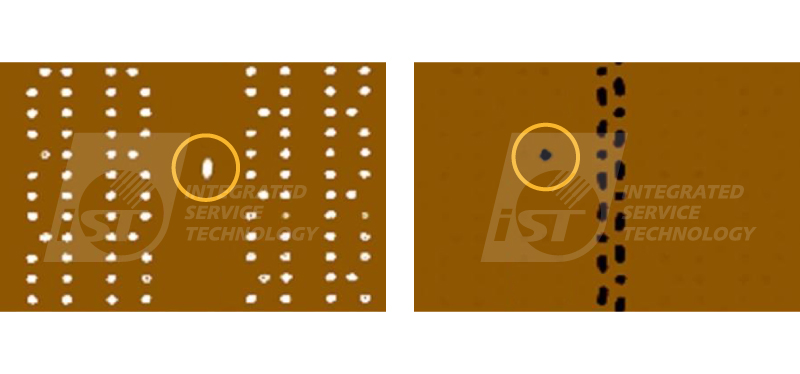

當逐層去除(Layer by Layer)過程當中,除利用電子顯微鏡(SEM) 於故障點區域進行VC (Voltage Contrast)的電性確認與金屬導線型態觀察外,亦可搭配導電原子力顯微鏡(Conductive Atomic Force Microscopy簡稱C-AFM)快速掃描該異常區域,以獲得該區域電流分布圖(Current map)(圖五),並量測該接點對矽基板(Si Substrate)的電性表現,進而確認該區域是否有漏電/開路等電性異常問題。

《圖五(左)》C-AFM異常分析結果圖。圖五(左): 外加正電壓(+1V)時的Current map異常電性發生;

《圖五(左)》C-AFM異常分析結果圖。圖五(左): 外加正電壓(+1V)時的Current map異常電性發生;

《圖五(右)》外加負電壓(-1V)時的Current map異常電性發生(黃圈處)。圖/宜特科技

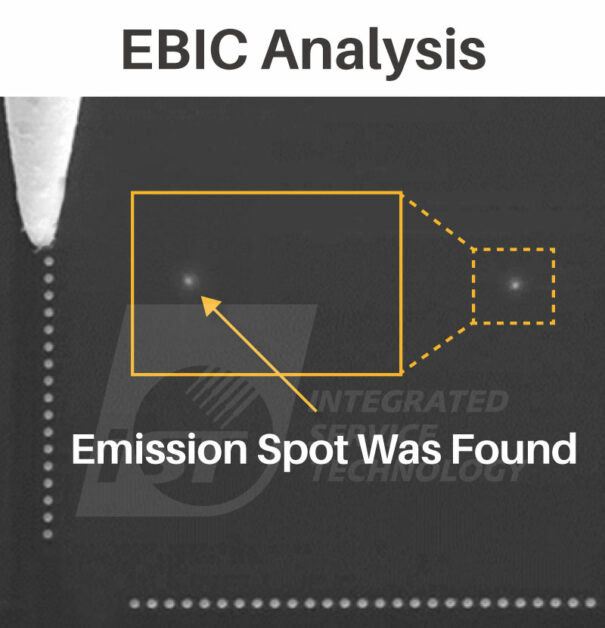

在完成C-AFM分析後,若有相關疑似異常路徑需要進一步進行電性量測與定位,可使用奈米探針電性量測(Nano-Prober)進行更精準的異常點定位分析,包括電子束感應電流(EBIC , Electron Beam Induced Current)、電子束吸收電流(EBAC, Electron Beam Absorbed Current)、與電子束感應阻抗偵測(EBIRCH , Electron Beam Induced Resistance Change)等定位法。而Nano-Prober亦可針對電晶體進行電性量測,如Vt、 IdVg、IdVd等基本參數獲取(圖六)。

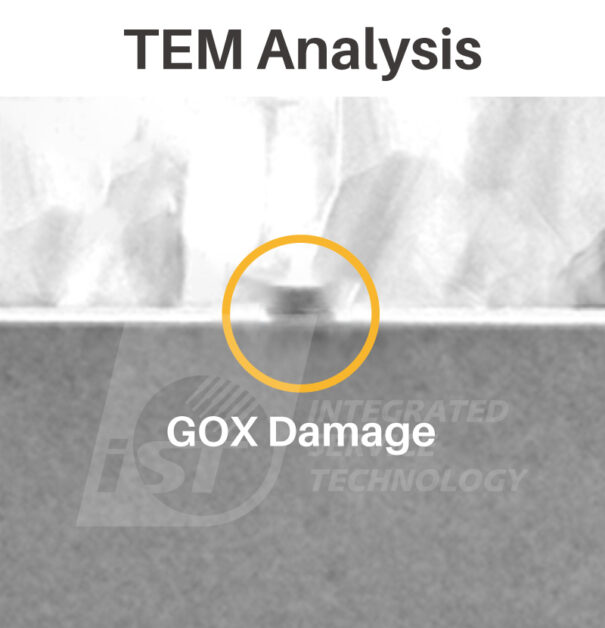

當透過上述分析手法精準找到異常點後,亦可再透過雙束聚焦離子束(Dual-beam FIB,簡稱DB-FIB)或是穿透式電子顯微鏡(Transmission Electron Microscopy,簡稱TEM)來對異常點進行結構確認,以釐清失效原因(圖七)。

《圖六》EBIC分析結果圖。圖/宜特科技

《圖六》EBIC分析結果圖。圖/宜特科技

《圖七》TEM分析結果圖。圖/宜特科技

《圖七》TEM分析結果圖。圖/宜特科技

(四) 超音波顯微鏡 (Scanning Acoustic Tomography,簡稱SAT)分析:於背照式(BSI)/堆疊式(Stacked) CIS晶圓對接製程的應用

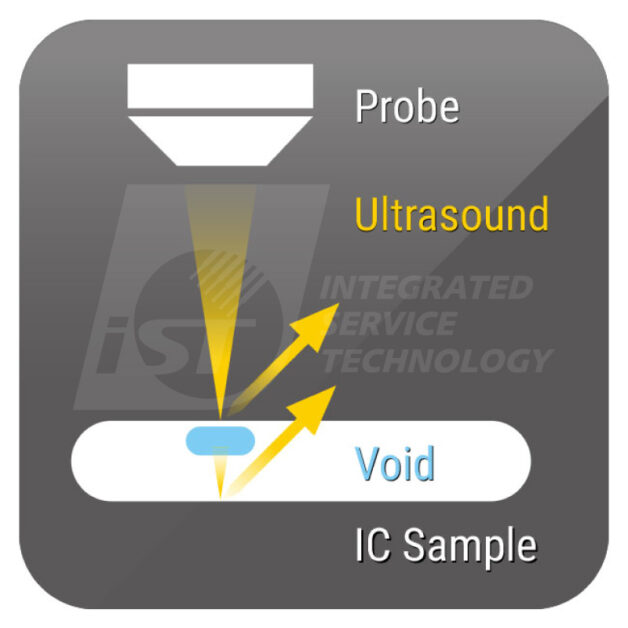

超音波顯微鏡(SAT)

超音波顯微鏡(SAT)為藉由超音波於不同密度材料反射速率及回傳能量不同的特性來進行分析,當超音波遇到不同材料的接合介面時,訊號會部分反射及部分穿透,但當超音波遇到空氣(空隙)介面時,訊號則會100%反射,機台就會接收這些訊號組成影像。

超音波顯微鏡(SAT)原理圖。圖/宜特科技

超音波顯微鏡(SAT)原理圖。圖/宜特科技

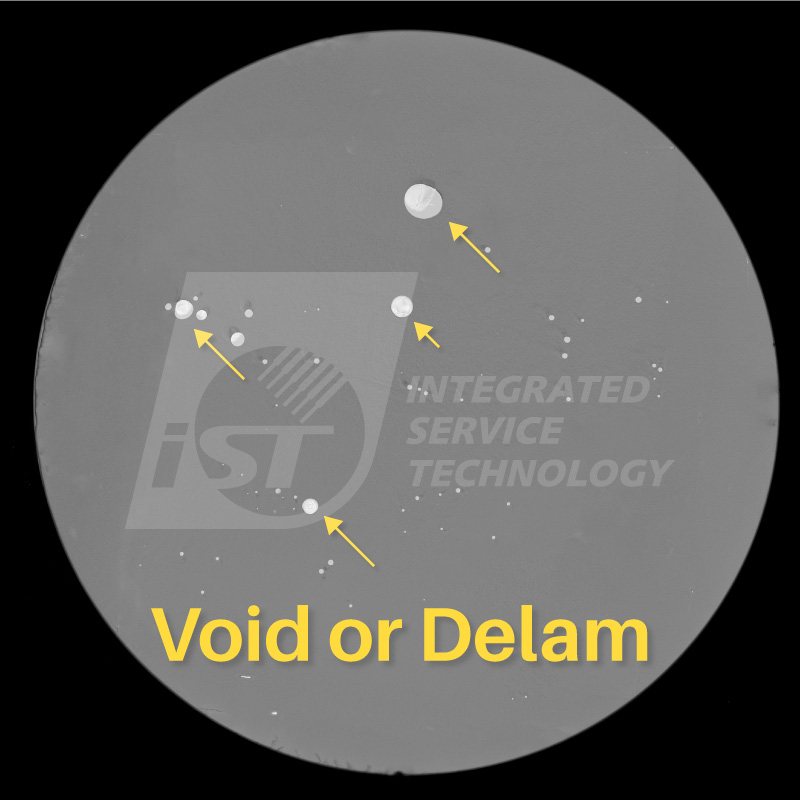

在背照式(BSI)與堆疊式(Stacked) CIS製程中晶圓與晶圓對接(bonding)製程中,SAT可作為偵測晶圓與晶圓之間接合不良造成存在空隙的重要利器(圖八)。

《圖八》透過超音波顯微鏡(SAT),找到晶圓與晶圓對接(bonding)之鍵合空隙位置。圖/宜特科技

《圖八》透過超音波顯微鏡(SAT),找到晶圓與晶圓對接(bonding)之鍵合空隙位置。圖/宜特科技

半導體堆疊技術的蓬勃發展,加上人們對影像感測器在消費性電子、車用電子、安控系統等應用,功能需求大幅度增加,CIS未來將繼續進化,無論是晶圓級對接的製程穩定度分析,或是堆疊式(Stacked) CIS故障分析,都可以透過宜特實驗室豐富的分析手法,與一站式整合服務精準地分析、加速產品開發、改善產品品質。

本文出自www.istgroup.com。

ufabet

มีเกมให้เลือกเล่นมากมาย: เกมเดิมพันหลากหลาย ครบทุกค่ายดัง

ufabet

มีเกมให้เลือกเล่นมากมาย: เกมเดิมพันหลากหลาย ครบทุกค่ายดัง